### **Digital Integrated Circuits**

Monolithic Silicon

## Developmental Types TA6889, TA6890

## RCA COS/MOS Microprocessor (COSMAC)

TA6889 – Microprocessor Control IC TA6890 – Microprocessor Register IC

#### Features:

- Static COS/MOS circuitry, no minimum clock frequency

- Full military temperature range

- High noise immunity, wide operating voltage range

- TTL compatibility

- 8-bit parallel organization with bidirectional data bus

- Built-in program-load facility

- Any combination of standard RAM/ROM via common interface

- Direct memory addressing up to 65,536 bytes

- Flexible programmed I/O mode

- Program interrupt mode

- On-chip DMA facility

- Four I/O flag inputs directly testable by Branch instructions

- One-byte instruction format with two machine cycles for each instruction

- 59 easy-to-use instructions

- 16 x 16 matrix of registers for use as multiple program counters, data pointers, or data registers

The RCA Dev. Types TA6889 and TA6890, as an integral circuit pair, form a microprocessor (COSMAC) that is an LSI COS/MOS, 8-bit, register-oriented central processing unit (CPU) designed for use as a general-purpose computing or control element. The COSMAC architecture was designed with emphasis on the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can be realized.

#### Applications:

Point-of-sale terminals

Automotive controls

Entertainment/Educational devices

Communication controllers

Small business machines

Intelligent computer peripherals

Process monitors and controllers

Industrial controllers

Smart instruments

Traffic controls

Military/Aerospace applications

TA6889, TA6890 COSMAC Microprocessol

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| -65 to +150°C |   |  |  |  |     |    |      | NGE         | RATURE RAN        | GE-TEMPER              | STOF |  |

|---------------|---|--|--|--|-----|----|------|-------------|-------------------|------------------------|------|--|

| -55 to +125°C |   |  |  |  |     |    |      | RANGE .     | ERATURE R         | TING-TEMPE             | OPER |  |

|               |   |  |  |  |     |    |      | Ξ           | AGE RANGE         | PLY-VOLTA              | DC S |  |

| -0.5 to +15 V |   |  |  |  |     |    |      |             | ν <sub>DD</sub> ) | , (V <sub>CC</sub> ≤ V | ٧٢   |  |

| 200 mW        |   |  |  |  |     |    |      | ACKAGE)     | ION (PER PAC      | E DISSIPATION          | DEVI |  |

|               |   |  |  |  | i): | NG | ERI  | NG SOLDE    | JRE (DURING       | <b>TEMPERATU</b>       | LEA  |  |

|               |   |  |  |  | )   | nm | 79 m | (1.59 ± 0.7 | ± 1/32 inch (1    | istance 1/16 ±         | At   |  |

| 265°C         | _ |  |  |  |     |    |      |             | 10 seconds ma     |                        |      |  |

<sup>▲</sup>All voltage values are referenced to V<sub>SS</sub> terminal.

#### OPERATING CONDITIONS AT TA = 25°C

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges.

| Characteristic                                          | v <sub>DD</sub>              | Min.            | Тур. | Max.            | Units |

|---------------------------------------------------------|------------------------------|-----------------|------|-----------------|-------|

| Supply Voltage Range                                    | _                            | 4               | 10   | 12              | ٧     |

| Maximum Input<br>Voltage Swing                          | _                            | V <sub>SS</sub> | -    | v <sub>DD</sub> | V     |

| Recommended Input<br>Voltage Swing                      | _                            | V <sub>SS</sub> | _    | v <sub>cc</sub> | ٧     |

| Clock Input Rise<br>or Fall Time                        | 4-12 V                       |                 | _    | 15              | μs    |

| Instruction Time (Using memory having 1-µs access time) | 10 V<br>V <sub>CC</sub> =5 V | _               | 8    | _               | μs    |

| Clock Input Frequency                                   | 10 V                         | DC              | 2    | _               | MHz   |

#### Notes:

#### ELECTRICAL CHARACTERISTICS @ T<sub>A</sub> = 25°C; V<sub>SS</sub> = Gnd; t<sub>r</sub>,t<sub>f</sub> = 20 ns

|                                                                     | TEST C                                          | ONDITIO              | vs                   |                   |       |  |

|---------------------------------------------------------------------|-------------------------------------------------|----------------------|----------------------|-------------------|-------|--|

| CHARACTERISTIC                                                      |                                                 | v <sub>cc</sub><br>v | V <sub>DD</sub><br>V | TYPICAL<br>VALUES | UNITS |  |

| STATIC                                                              |                                                 |                      |                      |                   |       |  |

| Quiescent Device                                                    |                                                 | 5                    | 5                    | 11                | mA    |  |

| Current, IL                                                         |                                                 | 10                   | 10                   | 2                 |       |  |

| Output Voltage:<br>Low Level, V <sub>OL</sub>                       | Driving<br>COS/MOS                              | _                    |                      | 0                 | V     |  |

| High Level, V <sub>OH</sub>                                         | Loads                                           | _                    | -                    | V <sub>CC</sub>   |       |  |

| Output Drive Current:<br>N-Channel (Sink),<br>I <sub>D</sub> N      | V <sub>O</sub> =0.4 V                           | 5                    | 10                   | 5                 |       |  |

| 2.01                                                                | V <sub>O</sub> =4.6 V                           | 5                    | 10                   | 1.5               | mA    |  |

| P-Channel (Source),<br>I <sub>D</sub> P                             | 0.5.1/                                          | 5                    | 5                    | 5                 | mA    |  |

|                                                                     | V <sub>O</sub> =2.5 V                           | 5                    | 10                   | 15                |       |  |

| Noise Immunity<br>(Any Input)<br>VNL                                | V <sub>O</sub> =0.8 V                           | 5                    | 5                    | 2.25              | V     |  |

| V <sub>NH</sub>                                                     | V <sub>O</sub> =4.2 V                           | 5                    | 5                    | 2.25              | 1     |  |

| DYNAMIC                                                             |                                                 |                      |                      |                   |       |  |

| Average Device<br>Dissipation (Total<br>Both Units), P <sub>d</sub> | f <sub>CL</sub> =2 MHz<br>C <sub>L</sub> =50 pF | 5                    | 10                   | 60                | mW    |  |

| Average Device<br>Current (I <sub>dd</sub> + I <sub>cc</sub> )      |                                                 | 5                    | 10                   | 6.5               | mA    |  |

|                                                                     | F:- 1                                           | 5                    | 5                    | 1500              | ns    |  |

| Settling Time, t <sub>s</sub>                                       | Fig. 1                                          | 5                    | 10                   | 750               | 113   |  |

| Transition Time:                                                    | C <sub>I</sub> =50 pF                           | 5                    | 10                   | 30                | ns    |  |

| tTLH                                                                |                                                 | 5                    | 10                   | 80                |       |  |

| Average Input<br>Capacitance                                        | А                                               | ny Input             |                      | 5                 | pF    |  |

<sup>1.</sup> V<sub>CC</sub> ≤ V<sub>DD</sub>

<sup>2.</sup> Because a large number of nodes may be switching simultaneously, a 0.1  $\mu$ F by-pass capacitor is recommended in the power supply.

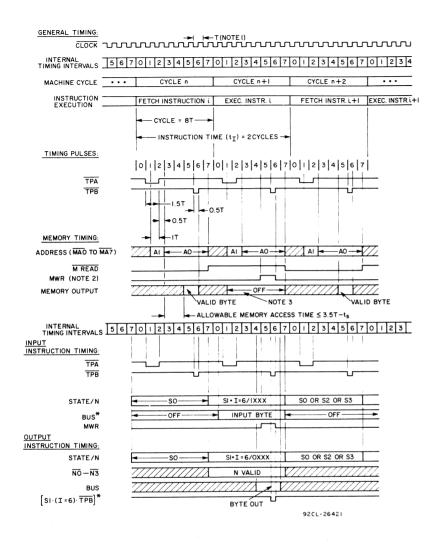

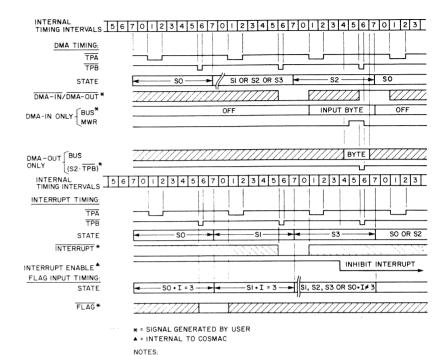

Fig. 1-COSMAC Timing.

92CL - 26422

Fig. 1-COSMAC Timing (Cont'd).

I. MINIMUM T DETERMINED BY VDD -- NO MAXIMUM T

3. MEMORY OUTPUT "OFF" INDICATES HIGH-IMPEDANCE CONDITION.

4. SHADING INDICATES "DON'T CARE" OR INTERNAL DELAYS DEPENDING ON

2. MEMORY WRITE PULSE WIDTH (MWR) ≈ 1.5 T

VDD AND THE CLOCK SPEED.

#### - BUS 4 BUS 2 BUS 5 BUS I BUS 6 BUSO BUS 7 - V**s**s I/O COMMANDS - FFI BUS 4 DATA I/O FLAGS DATA BUS - EF2 BUS 2 BUS 5 - EF3 N3 BUS 6 BUS I - ĒF4 - BUS O BUS 7 - DMA OUT MAO INTERRUPT MAI - DMA IN MA2 MEMORY ADDRESS LINES - CLEAR CONTROL MA3 CLOCK - LOAD MA4 TIMING PULSES TPB - I.C.(NOTE 4) MA5 - SCI MAG - <u>sco</u> 23 MA7 22 - M READ CLEAR + ٧ss VSS . 21 TOP VIEW 9205-26417 9205-26418

#### Package Interconnections

|                |   |    |    |    |    | *  | *  | *  | *  | *  |    | *  | *  |    |    |    |    |    |    |

|----------------|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| TA6889 Pin No. | 1 | 2  | 3  | 4  | 5  | 10 | 11 | 12 | 13 | 14 | 16 | 18 | 21 | 27 | 36 | 37 | 38 | 39 | 40 |

| TA6890 Pin No. | 1 | 27 | 26 | 25 | 24 | 17 | 18 | 19 | 20 | 23 | 22 | 21 | 16 | 15 | 5  | 4  | 3  | 2  | 28 |

\* These pins are for interchip connections only

#### Notes:

- 1. Any unused input pins should be connected to VDD or VCC.

- 2. The Data Bus lines are bi-directional and have three-state outputs. They may be individually connected to  $V_{CC}$  through external pull-up resistors (22 k $\Omega$  recommended) to prevent floating inputs.

- All inputs have the same noise immunity and level-shifting capability.

All outputs have the same drive capability whether they have three-state outputs or not.

- 4. Pin 25 of TA6889 is used for an internal connection-do not use.

Fig. 2-Terminal Assignment Diagrams.

#### **DIMENSIONAL OUTLINES**

#### TA6890 28-Lead Ceramic

| IA68        | 889    |

|-------------|--------|

| 40-Lead C   | eramic |

| MILLIMETERS | INCHE  |

| DIM.   | MILLIM | IETERS | INCHES     |       |  |  |

|--------|--------|--------|------------|-------|--|--|

| Ulivi, | MIN.   | MAX.   | MIN.       | MAX.  |  |  |

| Α      | 35.06  | 36.06  | 1.380      | 1.420 |  |  |

| С      | 2.16   | 3.68   | 0.085      | 0.145 |  |  |

| D      | 0.43   | 0.56   | 0.017      | 0.023 |  |  |

| F      | 1.27   | REF.   | 0.050 REF. |       |  |  |

| G      | 2.54   | BSC    | 0.100 BSC  |       |  |  |

| н      | 0.76   | 1.78   | 0.030      | 0.070 |  |  |

| J      | 0.20   | 0.30   | 0.008      | 0.012 |  |  |

| K      | 3.18   | 4.45   | 0.125      | 0.175 |  |  |

| L      | 14.74  | 15.74  | 0.580      | 0.620 |  |  |

| М      | -      | 70     | -          | 70    |  |  |

| Р      | 0.64   | 1.27   | 0.025      | 0.050 |  |  |

|        |        |        |            |       |  |  |

| DIM.    | MILLIN | METERS | INCHES     |       |  |  |

|---------|--------|--------|------------|-------|--|--|

| O i ivi | MIN.   | MAX.   | MIN.       | MAX.  |  |  |

| Α       | 50.30  | 51.30  | 1.980      | 2.020 |  |  |

| С       | 2.42   | 3.93   | 0.095      | 0.155 |  |  |

| D       | 0.43   | 0.56   | 0.017      | 0.023 |  |  |

| F       | 1.27   | REF.   | 0.050 REF. |       |  |  |

| G       | 2.54   | BSC    | 0.100 BSC  |       |  |  |

| н       | 0.76   | 1.78   | 0.030      | 0.070 |  |  |

| J       | 0.20   | 0.30   | 0.008      | 0.012 |  |  |

| К       | 3.18   | 4.45   | 0.125      | 0.175 |  |  |

| L       | 14.74  | 15.74  | 0.580      | 0.620 |  |  |

| M       | -      | 70     | -          | 70    |  |  |

| Р       | 0.64   | 1.27   | 0.025      | 0.050 |  |  |

| N       | 4      | 0      | 4          | 10    |  |  |

# N

#### .....

- Leads within 0.13 mm (0.005) radius of true position

- at maximum material condition.

2. Dimension "L" to center of leads when formed parallel

- 3. When this device is supplied solder-dipped, the maximum lead thickness (narrow portion) will not exceed 0.013 in.

(0.33 mm)

The following is a brief description of the COSMAC microprocessor. For more detailed information see the following two publications:

- "User Manual for the COSMAC Microprocessor" – MPM-101

- 2. "Program Development Guide for the COSMAC Microprocessor" MPM-102

The RCA Microprocessor (COSMAC) is implemented by two COS/MOS chips. The Dev. No. TA6889, in a 40-lead dual-in-line ceramic package, contains the arithmetic logic unit (ALU), control logic, and various working registers. The Dev. No. TA6890, in a 28-lead dual-in-line ceramic package, contains the multi-purpose 16 x 16 register array, a buffer register, associated controls, and an increment/decrement circuit associated with the register array.

COSMAC is a static system; therefore, the clock input frequency can be chosen to interface with memories or I/O devices having speeds that vary over a wide range.

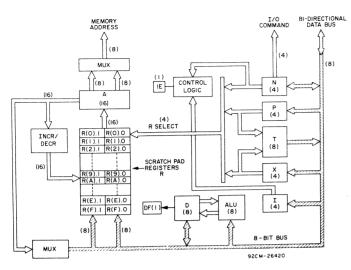

#### Architecture

The COSMAC block diagram is shown in Fig. 3. The principal feature of this system is a register array (R) consisting of sixteen, 16-bit scratchpad registers. Individual registers in the array (R) are designated (selected) by a 4-bit binary code from one of the 4-bit registers labeled N, P, and X. The contents of any register, through the 16-bit buffer register A, can be directed to any one of the following three paths:

- the external memory (multiplexed, higher-order byte first, on to 8 memory address lines);

- 2. the D register (either of the two bytes can be gated to D);

- 3. the increment/decrement circuit where it is increased or decreased by one and stored back in the selected 16-bit register.

The three paths, depending on the nature of the instruction, may operate independently or in various combinations in the same machine cycle.

Fig. 3-COSMAC Block Diagram.

Every COSMAC instruction consists of two 8-clock-pulse machine cycles. The first cycle is the fetch cycle, and the second is the execute cycle. During the fetch cycle the four bits in the P designator select one of the 16 registers R(P) as the current program counter. This selected R(P) contains the address of the memory location from which the instruction is to be fetched. When the instruction is read out from the memory, the higher-order 4 bits of the instruction byte are loaded into the I register and the lowerorder 4 bits are fed to the N register. The content of the program counter is automatically incremented by one so that R(P) is now "pointing" to the next byte in the memory.

The X designator selects one of the 16 registers R(X) to "point" to the memory for an operand (or data).

The N designator can perform the following five functions depending on the type of instruction fetched:

- designate one of the 16 registers in R to be acted upon during register operations:

- indicate to the I/O devices a command code or device-selection code for peripherals;

- indicate the specific operation to be executed during the ALU instructions, types of tests to be performed during the Branch instructions, or operating modes of interrupt handling instructions;

- indicate the value to be loaded into P to designate a new register to be used as the program counter R(P);

- indicate the value to be loaded into X to designate a new register to be used as data pointer R(X).

The registers in R can be assigned by a programmer in three different ways: as program counters, as data pointers, or as scratch-pad locations (data registers) to hold two bytes of data.

#### **Program Counters**

Any register can be the main program counter; the address of the selected register is held in the P designator. The other registers in R can be used as subroutine program counters. By a single instruction the contents of the P register can be changed to effect a "call" to a subroutine. When interrupts are being serviced, register R(1) is used as the program counter for the interrupt servicing routine. At all other times the register designated as program counter is at the discretion of the user.

#### **Data Pointers**

The registers in R may be used as data pointers to indicate where the data (operand) is located in the memory. The register designated by X [i.e., R(X)] points to the operand for the following instructions (see Table I):

- 1. ALU operations F0 through F7;

- 2. output instructions 60 through 67;

- 3. input instructions 68 through 6F.

The register designated by N [i.e., R(N)] points to the operand for the "load D from memory" instruction 4N and the "store D" instruction 5N. The register designated by P (i.e., the program counter) is used as the data pointer for ALU instructions F8 through FF. During these instruction executions the operation is referred to as "data immediate".

Another important use of R as a data pointer supports the built-in Direct-Memory-Access (DMA) function. When a DMA-in or DMAout request is received, one machine cycle is "stolen". This operation occurs at the end of the execute machine cycle in the current instruction. Register R(O) is always used as the data pointer during the DMA operation (hardwired). The data is read from or written into the memory location (depending on out or in request) pointed to by the R(O) register. At the end of the transfer, R(O) is incremented by one so that the processor is ready to act upon the next DMA byte transfer request. This feature in the COSMAC architecture saves a substantial amount of logic when fast exchanges of blocks of data are required, such as with magnetic discs of during CRTdisplay-refresh cycles.

A program load facility, using this DMA channel, is provided to enable users to load programs into the memory. This facility provides a simple, one-step means for initially entering programs into the microprocessor system and eliminates the requirement for specialized "bootstrap" ROM's.

#### Data Registers

When registers in R are used to store bytes of data, four instructions are provided which allow D to receive from or write into either the higher-order- or lower-order-byte portions of the register designated by N. By this mechanism (together with loading by data immediate) program pointer and data pointer designations are initiated. Also, this technique allows scratch-pad registers in R to be used to hold general data. Some simple controllers can be designed which use no RAM (random

access memory)—the 32-byte capacity of R suffices for program counting, data pointing, and data storing.

#### Interrupt Servicing

Register R(1) is always used as the program counter whenever interrupt servicing is effected. When an interrupt request comes in and the interrupt is allowed by the designer (again, nothing takes place until the end of the current execute machine cycle of the instruction is completed), the contents of the P and X registers are stored in the temporary register T, and P and X are set to new values; hex digit 1 in P and hex digit 2 in X. Interrupt enable is automatically deactivated to inhibit further interruptions. The interrupt routine is now in control; the contents of T are saved by means of a single instruction (78) in the memory location pointed to by R(X), where X = 2. At the conclusion of the interrupt, the routine restores the pre-interrupted values of P and X with a single instruction. The interrupt-enable flip-flop can be activated to permit further interrupts or can be disabled to prevent them.

#### **COSMAC Register Summary**

| D    | 8 Bits  | Data Register (Accumulator)                     |

|------|---------|-------------------------------------------------|

| DF   | 1 Bit   | Data Flag (ALU Carry)                           |

| R    | 16 Bits | 1 of 16 Scratchpad Registers                    |

| Р    | 4 Bits  | Designates which register is<br>Program Counter |

| X    | 4 Bits  | Designates which register is<br>Data Pointer    |

| N    | 4 Bits  | Low-order Instruction Digit                     |

| I    | 4 Bits  | High-order Instruction Digit                    |

| Т    | 8 Bits  | Holds old X, Pafter Inter-<br>rupt              |

| IE . | 1 Bit   | Interrupt Enable                                |

Interrupt Action: X and P are stored in T after executing current instruction; designator P is set to 1; designator X is set to 2; interrupt enable is reset to 0 (inhibit); and the interrupt request is serviced.

DMA Action: Finish executing current instruction; R(O) points to memory area for data transfer; data is loaded into or read out of memory; and increment R(O).

Note: In the event of concurrent DMA and INTERRUPT requests, DMA has priority.

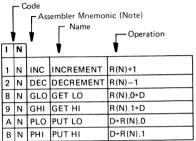

#### Instruction Set

The COSMAC instruction summary is given in Table I. Hexadecimal notation is used to refer to the 4-bit binary codes. Many of the instructions have been discussed in the Architecture section. Symbols used are:

R(W): Register designated by W, where W = N, or X, or P

R(W).0: Lower-order byte of R(W) R(W).1: Higher-order byte of R(W)

#### n Operation Notation

$M(R(N)) \rightarrow D;R(N) + 1$

This notation means: The memory byte pointed to by R(N) is loaded into D, and R(N) is incremented by 1.

#### Table I - Instruction Summary

#### Register Operations

N=0,1,2, ...,9,A,B, ...,E,F (Hexadecimal Notation)

#### Memory Reference

| ı | N |     |          |                  |

|---|---|-----|----------|------------------|

| 4 | N | LDA | LOAD ADV | M(R(N))→D;R(N)+1 |

| 5 | N | STR | STORE    | D→M(R(N))        |

#### **ALU Operations**

|   | ı | Ν |     |                |                                |

|---|---|---|-----|----------------|--------------------------------|

|   | F | 0 | LDX | LOAD BY X      | M(R(X))→D                      |

|   | F | 1 | OR  | OR             | M(R(X)) vD÷D                   |

|   | F | 2 | AND | AND            | M(R(X))·D→D                    |

|   | F | 3 | XOR | EXCL.OR        | M(R(X))⊕ D→D                   |

| * | F | 4 | ADD | ADD            | M(R(X))+D+D;C+DF               |

| * | F | 5 | SD  | SUBTRACT D     | M(R(X))-D+D;C+DF               |

| * | F | 6 | SHR | SHIFT<br>RIGHT | SHIFT D RIGHT;<br>LSB+DF;0+MSB |

| * | F | 7 | SM  | SUBTRACT M     | D-M(R(X))+D;C+DF               |

|   | F | 8 | LDI | LOAD IMM       | M(R(P))→D;R(P)+1               |

|   | F | 9 | ORI | OR IMM         | M(R(P)) vD→D;R(P)+1            |

|   | F | Α | ANI | AND IMM        | M(R(P)) • D → P; R(P) + 1      |

|   | F | В | XRI | EXCL.OR<br>IMM | M(R(P))⊕ D+D;<br>R(P)+1        |

| * | F | С | ADI | ADD IMM        | M(R(P))+D→D;<br>C→DF;R(P)+1    |

| ٠ | F | D | SDI | SUBT D IMM     | M(R(P))—D→D;<br>C→DF;R(P)+1    |

| * | F | F | SMI | SUBT M IMM     | D-M(R(P))→D;<br>C→DF;R(P)+1    |

## Branching

| 0 | BR                                             | UNCOND.BR.                                                    | $M(R(P))\rightarrow R(P).0$                                                                                                                                                                             |

|---|------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | BZ                                             | BR.IF D=00                                                    | M(R(P))→R(P).0<br>IF D=00/R(P)+1                                                                                                                                                                        |

| 3 | BDF                                            | BR.IF DF=1                                                    | M(R(P))→R(P).0<br>IF DF=1/R(P)+1                                                                                                                                                                        |

| 4 | В1                                             | BR.IF EF1=1                                                   | M(R(P))+R(P).0<br>IF EF1=1/R(P)+1                                                                                                                                                                       |

| 5 | B2                                             | BR.IF EF2=1                                                   | M(R(P))→R(P).0<br>IF EF2=1/R(P)+1                                                                                                                                                                       |

| 6 | В3                                             | BR.IF EF3=1                                                   | M(R(P))→R(P).0<br>IF EF3=1/R(P)+1                                                                                                                                                                       |

| 7 | B4                                             | BR.IF EF4=1                                                   | M(R(P))→R(P).0<br>IF EF4=1/R(P)+1                                                                                                                                                                       |

| 8 | SKP                                            | SKIP                                                          | R(P)+1                                                                                                                                                                                                  |

| Α | BNZ                                            | BR.IF D≠00                                                    | M(R(P))→R(P).0<br>IF D≠00/R(P)+1                                                                                                                                                                        |

| В | BNF                                            | BR.IF DF=0                                                    | M(R(P))→R(P).0<br>IF DF=0/R(P)+1                                                                                                                                                                        |

| С | BN1                                            | BR.IF EF1=0                                                   | M(R(P))→R(P).0<br>IF EF1=0/R(P)+1                                                                                                                                                                       |

| D | BN2                                            | BR.IF EF2=0                                                   | M(R(P))→R(P).0<br>IF EF2=0/R(P)+1                                                                                                                                                                       |

| E | BN3                                            | BR.IF EF3=0                                                   | M(R(P))→R(P).0<br>IF EF3=0/R(P)+1                                                                                                                                                                       |

| F | BN4                                            | BR.IF EF4=0                                                   | M(R(P))→R(P).0<br>IF EF4=0/R(P)+1                                                                                                                                                                       |

|   | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>A<br>B<br>C | 3 BDF 4 B1 5 B2 6 B3 7 B4 8 SKP A BNZ B BNF C BN1 D BN2 E BN3 | 2 BZ BR.IF D=00 3 BDF BR.IF DF=1 4 B1 BR.IF EF1=1 5 B2 BR.IF EF2=1 6 B3 BR.IF EF3=1 7 B4 BR.IF EF4=1 8 SKP SKIP A BNZ BR.IF D≠00 B BNF BR.IF D≠00 C BN1 BR.IF EF1=0 D BN2 BR.IF EF2=0 E BN3 BR.IF EF3=0 |

#### Control

|   | N |     |         |                                              |

|---|---|-----|---------|----------------------------------------------|

| 0 | 0 | IDL | IDLE    | WAIT FOR<br>INTERRUPT/<br>DMA-IN/<br>DMA-OUT |

| D | N | SEP | SET P   | N→P                                          |

| E | N | SEX | SET X   | N→X                                          |

| 7 | 0 | RET | RETURN  | M(R(X))→ X, P;<br>R(X)+1;1→IE                |

| 7 | 1 | DIS | DISABLE | M(R(X))→X, P;<br>R(X)+1;0→IE                 |

| 7 | 8 | SAV | SAVE    | T→M(R(X))                                    |

Input-Output Byte Transfer

| ı               | N |       |          |                            |  |

|-----------------|---|-------|----------|----------------------------|--|

| 6               | 0 | OUT 0 | OUTPUT 0 | M(R(X))→BUS;<br>R(X)+1;N=0 |  |

| 6               | 1 | OUT 1 | OUTPUT 1 | M(R(X))→BUS;<br>R(X)+1;N=1 |  |

| 6               | 2 | OUT 2 | OUTPUT 2 | M(R(X))→BUS;<br>R(X)+1;N=2 |  |

| 6               | 3 | OUT 3 | OUTPUT 3 | M(R(X))→BUS;<br>R(X)+1;N=3 |  |

| 6               | 4 | OUT 4 | OUTPUT 4 | M(R(X))→BUS;<br>R(X)+1;N=4 |  |

| 6               | 5 | OUT 5 | OUTPUT 5 | M(R(X))→BUS;<br>R(X)+1;N=5 |  |

| 6               | 6 | OUT 6 | OUTPUT 6 | M(R(X))→BUS;<br>R(X)+1;N=6 |  |

| 6               | 7 | OUT 7 | OUTPUT 7 | M(R(X))→BUS;<br>R(X)+1;N=7 |  |

| 6               | 8 | INP 0 | INPUT 0  | BUS→M(R(X));<br>N=8        |  |

| 6               | 9 | INP 1 | INPUT 1  | BUS→M(R(X));<br>N=9        |  |

| 6               | Α | INP 2 | INPUT 2  | BUS→M(R(X));<br>N=A        |  |

| 6               | В | INP 3 | INPUT 3  | BUS→M(R(X));<br>N=B        |  |

| 6               | С | INP 4 | INPUT 4  | BUS→M(R(X));<br>N=C        |  |

| 6               | D | INP 5 | INPUT 5  | BUS→M(R(X));<br>N=D        |  |

| 6               | E | INP 6 | INPUT 6  | BUS→M(R(X));<br>N=E        |  |

| 6               | F | INP 7 | INPUT 7  | BUS→M(R(X));<br>N=F        |  |

| Memory and Inni |   |       |          |                            |  |

\*These are the only operations that modify DF. DF is set or reset by an ALU carry during add or subtract. Subtraction is by 2's complement:  $A-B=A+\overline{B}+1$ .

Note: This type of abbreviated nomenclature is used when programs are designed with the aid of the COSMAC Assembler Simulator/Debugger System, which is available on commercial timesharing systems. Refer to "Program Development Guide for the COSMAC Microprocessor" for details.

#### Test and Branch

The Test and Branch instructions can branch unconditionally, test for D=0 or D=1, test for DF=0 or DF=1, or can test the status of the four I/O flags. A "successful" branch loads the byte following the instruction into the lower-order byte position of the current program counter, effecting a branch within the current 256-byte "page" of memory. If the test to branch is not successful, the next instruction in sequence is executed.

#### Memory and Input/Output Device Interface

The COSMAC CPU, by providing a synchronous interface to the external controllers for I/O devices and memories, minimizes the

cost of interface controllers. The I/O interface is capable of supporting devices operating in polled, interrupt-driven, or direct-memory-access modes.

CLEAR

— A single short pulse is required. A momentary low on this line places COSMAC in a repeating IDLE cycle with P = 0, R(O) = 0000 and IE = 1 (interrupt request allowed).

CLOCK

- Single-phase clock. A typical clock frequency is 2 MHz at VDD = 10 V. The clock is counted down internally to 8

clock pulses per machine cycle.

MA0 to MA7 (8 Memory Address Lines) The most significant 8 bits of the memory address is multiplexed out first on these lines and held in a latch in the memory system that is set by TPA. The 8 least significant bits are then multiplexed out on the same lines. The memory system always sees a 16-bit address within one memory-addressing cycle.

MWR (Write Pulse) — This pulse appears late in a memory-write cycle, after the address

lines have settled down.

M READ (Read Level)

— If a memory does not have a 3-state high-impedance output,

M READ is useful for driving memory/bus separator gates;

otherwise it is used to control 3-state outputs from the addressed

A repeating IDLE cycle represents an instruction halt. The processor will remain in this halt state until an I/O Request (INTERRUPT, DMA-IN, or DMA-OUT) is activated. When this request occurs, the IDLE cycle is terminated and the I/O request is serviced, and then the normal program is resumed. If a DMA request is used to bring the processor out of IDLE, it will increment the contents of R(O) by 1. The first instruction will, therefore, be fetched from memory location 0001 and not 0000. Thus, program execution begins at location 0001 with R(O) as the program counter.

memory. A low on MREAD indicates a read cycle; the low MREAD line enables the memory-output-bus gates during the read cycle (see Fig. 1, Timing Diagram).

BUS 0 to BUS 7

8-bit bidirectional data bus lines. These lines are used for transferring data between the memory, the microprocessor, and I/O devices.

NO to N3 (I/O Command)

Issued by an I/O instruction. They are interpreted by I/O control logic to move data between the memory and the I/O interface (discussed in the Architecture section). These lines can be used to issue command codes or device selection codes to the I/O devices (independently or combined with the memory byte on the data bus when an I/O instruction is executed).

EF0 to EF3 (4 Flags) These levels enable the I/O controllers to transfer status information to the processor. These levels can be tested by the conditional branch instructions. They can be used in conjunction with the INTERRUPT request line to establish interrupt priorities. These flags can also be used by I/O devices to "call the attention" of the processor, in which case the program must routinely test the status of these flag(s).

INTERRUPT, DMA-IN, DMA-OUT (3 I/O requests)

These requests were discussed in the Architecture section. They

are sampled by COSMAC in the interval between the leading edge

of TPB and the leading edge of TPA. The DMA request has a

higher priority than the INTERRUPT request.

SC0, SC1 (2 State Code Lines) These two lines indicate to the I/O controllers that the CPU is:

1) executing an I/O instruction, 2) acknowledging an interrupt request, 3) processing a DMA request, or 4) none of the above states. The levels of state code are tabulated below.

|                                      | State Code Lines |     |

|--------------------------------------|------------------|-----|

| State Type                           | SC1              | SC0 |

| S2 (DMA)                             | L                | Н   |

| S3 (Interrupt)                       | L                | L   |

| SO (Fetch)                           | Н                | Н   |

| S1 • [I=6] (I/O Instruction Execute) | Н                | L   |

| S1 · [I≠6] (All other instructions)  | Н                | Н   |

All these states last one machine cycle. They may be assumed valid at TPA.

TPA, TPB

(2 Timing Pulses)

Both occur once in each machine cycle (TPB follows TPA).

They are used by I/O controllers to interpret codes and to time interaction with the data bus. The trailing edge of TPA is used by the memory system to latch the higher-order byte of the 16-bit memory address.

LOAD

A level that holds the CPU in IDLE-DMA mode and allows an I/O device to load the memory without the need for a "bootstrap" loader. It modifies the IDLE condition so that DMA operation does not force execution of the next instruction.

V<sub>DD</sub>, V<sub>SS</sub>, V<sub>CC</sub> (Power Levels) The internal voltage supply V<sub>DD</sub> is isolated from the Input/

Output voltage supply V<sub>CC</sub> so that the processor may operate at maximum speed while interfacing with various external circuit technologies, including T<sup>2</sup>L at 5 volts. V<sub>CC</sub> must be less than or equal to V<sub>DD</sub>.

When incorporating RCA Solid State Devices in equipment, it is recommended that the designer refer to "Operating Considerations for RCA Solid State Devices", Form No. 1CE-402, available on request from RCA Solid State Division, Box 3200, Somerville, N.J. 08876.