# Programming Manual altair 680b

# **Table of Contents**

| I.   | INTRODUCTION page 3                                                                                                                                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II.  | SYSTEM DESCRIPTION page 5                                                                                                                                                                                                                                                                                                                              |

| III. | SOURCE LANGUAGE AND ADDRESSING MODES page 7                                                                                                                                                                                                                                                                                                            |

|      | Character Set page 7 Fields of the Source Statement page 8 Addressing Modes page 17 Assembler Directives page 25                                                                                                                                                                                                                                       |

| IV.  | INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                        |

|      | Condition Code Register Operations page 27 M6800 Instruction Set page 28-29 Hexadecimal Values of Machine Codes page 30 Octal Values of Machine Codes page 31 Decimal Values of Machine Codes page 32 Condition Code Register Instructions page 33 Number Systems page 34 Accumulator and Memory Operations page 38 Program Control Operations page 41 |

| ٧.   | ARITHMETIC OPERATIONS page 53                                                                                                                                                                                                                                                                                                                          |

|      | Number Systems                                                                                                                                                                                                                                                                                                                                         |

| VI.  | SAMPLE PROGRAMS page 77                                                                                                                                                                                                                                                                                                                                |

|      | APPENDIX A - Instruction Set APPENDIX B - Assembler Directives APPENDIX C - Input/Output Information                                                                                                                                                                                                                                                   |

Major portions of the Altair 680b Programming Manual have been reprinted by permission of Motorola Semiconductor Products, Inc., copyright 1975.

.

# I INTRODUCTION

The Altair 680b Programming Manual describes the format of the 680b assembly code source language and the 6800 MPU instruction set and addressing modes.

A brief overview of arithmetic programming techniques and some general purpose sample programs are also included.

This manual is in no way intended to be a beginning course in computer programming.

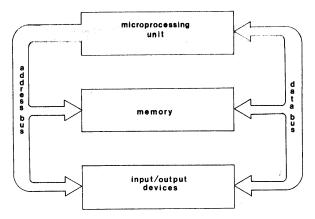

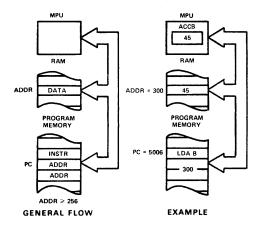

Figure 2-1

Microcomputer System Block Diagram

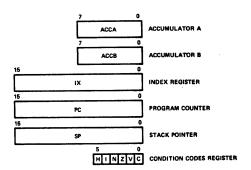

Figure 2-2. Programming Model of M6800

4

#### II SYSTEM DESCRIPTION

In order to program a computer in machine language or assembly code, it is necessary to have at least a block diagram level understanding of the computer hardware.

A general purpose microcomputer (see figure 2-1) consists of a microprocessing unit (MPU), a memory, and a number of input and output devices. These components are linked together by an address bus and a data bus.

The computer memory is used to store instructions and data for use by the MPU. In the 680b, the memory is organized into 8 bit words called bytes. Each memory byte is assigned a unique 16 bit address. This address is used by the MPU to gain access to the contents of a particular memory byte.

Input and output devices, such as Teletypes, CRT Terminals, and paper tape readers are used for communication between the computer and the external world. Each I/O device in a 680b system has one or more unique 16 bit addresses assigned to it.

The MPU is responsible for controlling the microcomputer system and performing all arithmetic and logic operations. The MPU must be told what steps to execute to perform a given task. This is accomplished by storing a program into the computer's memory. Once a program is stored in memory, a register in the MPU called the Program Counter (PC) is loaded with the address of the memory byte which contains the first instruction of the program. When the computer is put into the run mode, the MPU puts the address contained in the PC on the address bus and reads the contents of that location via the data bus. The instruction that has been read is executed after the PC is incremented to point to the next instruction.

This sequence is repeated until the processor is halted.

The 680b MPU is a Motorola M6800 which operates on 8-bit binary numbers presented to it via the data bus. A given number (byte) may represent either data or an instruction to be executed, depending on where it is encountered in a program. The M6800 has 72 unique instructions, however, it recognizes and takes action on 197 of the 256 possibilities that can occur using an 8-bit word length. This larger number of instructions results from the fact that many of the executive instructions have more than one addressing mode.

These addressing modes refer to the manner in which the program causes the MPU to obtain its instructions and data. The programmer must have a method for addressing the MPU's internal registers and all of the external memory locations. The complete executive instruction set and the applicable addressing modes are summarized in Figure 4-1, however, the addressing modes will be described in greater detail prior to introducing the instruction set in a later section. A programming model of the M6800 is shown in Figure 2-2. The programmable registers consist of: two 8-bit Accumulators; a 6-bit Condition Code Register; a Program Counter, a Stack Pointer, and an Index Register, each 16 bits long.

# III SOURCE LANGUAGE & ADDRESSING MODES

While programs can be written in the MPU's language, that is, binary numbers, there is no easy way for the programmer to remember the particular word that corresponds to a given operation. For this reason, instructions are assigned a three letter mnemonic symbol that suggests the definition of the instruction. The program is written as a series of source statements using this symbolic language and then translated into machine language. The translation can be done manually using an alphabetic listing of the symbolic instruction set such as that shown in Appendix A. More often, the translation is accomplished by means of a special computer program referred to as an assembler.

The source language for the M6800 microprocessing unit is built around 72 mnemonic instructions and 12 assembler directives. Section III deals with the details of the character set and format of the source language.

# CHARACTER SET

The characters used in the source language for the 680b assembler form a sub-set of ASCII (American Standard Code for Information Interchange, 1968). The ASCII Code is shown in Figure 3-1. The following characters are recognized by the assembler.

- 1. The alphabet A through  ${\sf Z}$ The integers 0 through 9

- 3. Four arithmetic operators:

- Characters used as special prefixes:

- (pounds sign) specifies the immediate mode of addressing

- (dollar sign) specifies a hexadecimal number

- (commercial at) specifies an octal number (percent) specifies a binary number

- ( apostrophe) specifies an ASCII literal character

- Characters used as special suffices:

- B (letter B) specifies a binary number

H (letter H) specifies a hexadecimal number

O (letter O) specifies an octal number

- Q (letter Q) specifies an octal number

- 6. Four separating characters:

- SPACE

- Horizontal TAB

- CR (carriage return)

- , (comma)

- The use of horizontal TAB is always optional, and can be replaced by SPACE.

- A comment in a source statement may include any characters with ASCII hexadecimal values from 20 (SP) through 5F ( ).

8. In addition to the above, the assembler has the capability of reading strings of characters and of entering the corresponding 7-bit ASCII code into specified locations in the memory. This capability is provided by the assembler directive FCC (See Appendix B). Any characters corresponding to ASCII hexadecimal values 20 (SP) through 5F (\_\_) can be processed. This kind of processing can also be done, for a single ASCII character, by using the immediate mode of addressing with an operand in the form "#C".

| BITS 4 thru 6 |    | 0   | 1   | 2  | 3 | 4 | 5 | 6 | 7   |

|---------------|----|-----|-----|----|---|---|---|---|-----|

|               | 0  | NUL | DLE | SP | 0 | @ | P |   | p   |

|               | 1  | SOH | DC1 | !  | 1 | Α | Q | a | q   |

|               | 2  | STX | DC2 | "  | 2 | В | R | b | r   |

|               | 3  | ETX | DC3 | #  | 3 | C | S | С | s   |

|               | 4  | EOT | DC4 | \$ | 4 | D | T | d | t   |

|               | 5  | ENQ | NAK | %  | 5 | E | U | е | u   |

| BITS 0 thru 3 | 6  | ACK | SYN | &  | 6 | F | V | f | v   |

|               | 7  | BEL | ETB | ,  | 7 | G | W | g | w   |

|               | 8  | BS  | CAN | (  | 8 | Н | X | h | x   |

|               | 9  | HT  | EM  | )  | 9 | I | Y | i | у   |

|               | Α  | LF  | SUB | *  | : | J | Z | j | z   |

|               | В  | VT  | ESC | +  | ; | K | [ | k | {   |

|               | C  | FF  | FS  | ,  | < | L | 1 | 1 | 1   |

|               | D  | CR  | GS  | -  | = | M | ] | m | . } |

|               | E  | SO  | RS  |    | > | N | ( | n | ~   |

|               | F_ | SI  | US  | 1  | ? | 0 |   | 0 | DEL |

Figure 3-1 ASCII Code

# FIELDS OF THE SOURCE STATEMENT

A source statement includes from one to four fields. From left to right, the four fields are:

(1) label (2) operator (mnemonic) (3) operand (4) comment

The comment is optional, and may be used in most source statements. Comments are intended for the convenience of the programmer, and to facilitate documentation of the program. A label is required for some statements which are involved in the definition of symbols and, in some cases, at the destinations of branches and jump instructions. An operand field may or may not be present depending on the nature of the operator. The mnemonic operator must be present in any statement except when the statement consists only of a comment.

With one optional exception (explained below), the successive fields within a statement are separated by,

either: one or more SPACE characters

or: horizontal TAB

The use of the horizontal TAB is hardware-dependent in that its availability will depend on the particular type of terminal in use. The SPACE bar may always be used rather than the TAB key.

#### CAUTION

A SPACE in the first character position of a source statement is used to indicate that a label is not included in the statement. A label, if used, must begin in the first character position of the source statement. It follows from the above that, when typing a source program into a file in which the statements are identified by line numbers, there will be only one space following the line number if the statement includes a label. Two or more spaces following the line number will indicate that a label is not used.

The exception to the foregoing rule relating to SPACE or horizontal TAB between the elements of a source statement applies to operators with dual addressing in the operand field (indicated by the column headed "Dual Operand" in Figure 3-2 and to certain other operators if they are functioning in the

"accumulator mode" of addressing (indicated by the column headed "ACCX" in Figure 3-2. In these cases, the first character of the operand field is either A or B (indicating accumulator A or B), and the second character is a SPACE. The programmer then has the option of omitting the SPACE between the operator and the operand field. This results in an apparent four-character format, as for example "ADCA", "ASRB", "STAA", "TSTB", and similarly.

### Label Field

An asterisk (\*) in the first character position of a statement causes the entire statement to become a comment. Otherwise, the comment will be preceded in the statement by one or more fields of the other three types, and the comment will occupy the last field in the statement.

Except in some cases when it is used with the mnemonic operator EQU (see below) a label always corresponds to a numerical address in the programmable system. It provides a means of referring to that address by using a symbol identical with the label. The address represented by the label (or symbol) may be that of an instruction in the machine code or of a location in the memory where data is stored.

|                   | (Duel Operand) | ACCX | Immediate | Direct | Extended | Indexed          | Inherent | Relative |                          | (Dual Operand) | ACCX | Immediate | Direct | Extended | pe xepui | Inherent         |

|-------------------|----------------|------|-----------|--------|----------|------------------|----------|----------|--------------------------|----------------|------|-----------|--------|----------|----------|------------------|

| ABA               |                | •    | •         | •      | •        | •                | 2        | •        | INC                      |                | 2    | •         | •      | 6        | 7        | •                |

| ADC               | X              | •    | 2         | 3      | 4        | 5                | •        | •        | INS                      |                | •    | •         | •      | •        | •        | 4                |

| ADD               | ×              | •    | 2         | 3      | -4       | 5                | •        | •        | INX                      |                | •    | •         | •      | •        | •        | 4                |

| AND               | x              | •    | 2         | 3      | 4        | 5<br>5<br>5<br>7 | •        | •        | JMP                      |                | •    | •         | •      | 3        | 4        | •                |

| ASL               |                | 2    | •         | •      | 6        | 7                | •        | •        | JSR                      |                | •    | •         | •      | 9        | 8        | •                |

| ASR               |                | 2    | •         | •      | 6        | 7                | •        | •        | LDA<br>LDS               | ×              | •    | 2         | 3      | 4        | 5        | •                |

| BCC               |                | •    | •         | •      | •        | •                | •        | 4        | LDS                      |                | •    | 3         | 4      | 5        | 6        | •                |

| BCS               |                | •    | •         | •      | •        | •                | •        | 4        | LDX                      |                | •    | 3         | 4      | 5        | 6        | •                |

| BEA               |                | •    | •         | •      | •        | •                | •        | 4        | LSR<br>NEG               |                | 2    | •         | •      | 6        | 7        | •                |

| BGE               |                | •    | •         | •      | •        | •                | •        | 4        | NEG                      |                |      | •         | •      | 6        | 7        | •                |

| BGT<br>BHI<br>BIT |                | •    | •         | •      | •        | •                | •        | 4        | NOF<br>ORA<br>PSH<br>PUL |                | •    | 2         | 3      | 4        | 5        | 2                |

| BHI               |                | •    | 2         | 3      | 4        | 5                | :        | 4        | OHA                      | \ X            | 4    | 2         |        |          | 9        | :                |

| BLE               | X              | •    |           |        |          | •                | :        | 4        | PUI                      | ,              | 4    | :         | :      | :        | :        | :                |

| BLS               |                | •    | :         | •      | •        | •                | •        | 4        | ROL                      |                | 2    | :         | •      | 6        | 7        |                  |

| BL T              |                | :    | :         | :      | •        | -                |          | 4        | ROF                      | i              | 2    | -         | -      | 6        | 7        |                  |

| BLT<br>BMI        |                | :    |           |        |          |                  |          | 4        | ROF<br>RTI               | •              | -    | •         |        | •        |          | 10               |

| BNE               |                | :    |           |        |          |                  |          | 4        | RTS                      |                | •    |           | •      | •        | •        | 5                |

| BPL               |                | •    | •         | •      | •        | •                | •        | 4        | SBA                      |                | •    | •         | •      | •        | •        | 5<br>2           |

| BPL<br>BRA        |                | •    | •         | •      | •        | •                | •        | 4        | SBC                      | ; х            | •    | 2         | 3      | 4        | 5        | •                |

| BSR               |                | •    |           | •      | •        | •                | •        | 8        | SEC                      | ;              | •    | •         | •      | •        | •        | 2                |

| BVC<br>BVS<br>CBA |                | •    | •         | •      | •        | •                | •        | 4        | SEI<br>SEV<br>STA        |                | •    | •         | •      | •        | •        | 2<br>2<br>2      |

| BVS               |                | •    | •         | •      | •        | •                | •        | 4        | SEV                      | ,              | •    | •         | •      | •        | •        | 2                |

| CBA               |                | •    | •         | •      | •        | •                | 2 2 2    | •        | STA                      | . х            | •    | •         | 4      | 5        | 6        | •                |

| CLC               |                | •    | •         | •      | •        | •                | 2        | •        | STS                      |                | •    | •         | 5      | 6        | 7        | •                |

| CLI               |                | •    | •         | •      | •        | •                |          | •        | STX                      |                | •    | •         | 5      | 6        | 7        | •                |

| CLR               |                | 2    | •         | •      | 6        | 7                | •        | •        | SUE                      | 3 x            | •    | 2         | 3      | 4        | 5        | •                |

| CLV<br>CMP        |                | •    | •         | •      | •        | •                | 2        | •        | SWI                      |                | •    | •         | •      | •        | •        | 12               |

| CMP               | ×              | •    | 2         | 3      | 4        | 5                | •        | •        | TAB                      |                | •    | •         | •      | •        | •        | 2                |

| COM               |                | 2    | •         | •      | 6<br>5   | 7<br>6           | •        | •        | TAP<br>TBA               |                | •    | •         | •      | •        | •        | 2                |

| CPX               |                | •    | 3         | 4      |          |                  | 2        | •        | TPA                      |                | •    | •         | •      | •        | •        | 2<br>2<br>2<br>2 |

| DAA<br>DEC<br>DES |                | 2    | •         | •      | 6        | 7                | •        | •        | TST                      | :              | 2    | •         | •      | 6        | 7        | •                |

| DEC               |                | 2    | •         | •      |          |                  | 4        | :        | TST<br>TSX<br>TSX        | •              | -    | -         | :      | 0        | <u>'</u> | 4                |

| DEX               |                | •    | •         | :      | :        | :                | 4        | -        | TSX                      | ;              | -    | -         | -      | -        | -        | 4                |

| EOR               | x              | :    | 2         | 3      | 4        | 5                | -        | -        | WAI                      |                | •    | :         | :      | :        | •        | 9                |

| LUN               | ^              | •    | -         | •      | -        | •                | •        | •        |                          |                | •    | •         | •      | •        | •        | •                |

NOTE: Interrupt time is 12 cycles from the end of the instruction being executed, except following a WA1 instruction. Then it is 4 cycles.

Figure 3-2 Instruction Addressing Modes and Execution Times (Times in Machine Cycles)

The following rules apply to labels:

- A label consists of from 1 to 6 alphanumeric characters.

- The first character of a label must be alphabetic.

- 3. A label must begin in the first character position of a statement.

- 4. All labels within a program must be unique.

- 5. A label must not consist of any one of the single characters A, B, or X. (These characters are reserved for special syntax, and refer to "accumulator A", "accumulator B", and "index register", respectively.)

Labels are used in source programs in the following cases:

- 1. A label may be included in any statement which is the destina

- a. Any of the conditional branch instructions: BCC BCS BEQ BGE BGT BHI BLE BLS BLT BMI BNE BPL BVC BVS

- b. The unconditional branch instruction: BRA, orc. The branch to a subroutine: BSR

Correspondingly, the operand field of the branch instruction would consist only of a single symbol which would be identical with the label at the destination. In the case of the instruction BSR, the symbol in the operand field, identical with the label at the destination, could be regarded as, in effect, the name of the subroutine.

A label may be included in any statement which is the destination of either of the instructions:

JMP (unconditional jump) or JSR (jump to subroutine)

when the instruction is being used in the extended mode of addressing.

Correspondingly, when used in the extended mode of addressing, the operand field of either of the instructions JMP and JSR  $\,$ would consist only of a symbol which would be identical with the label at the destination. For JSR, this could be regarded as, in effect, the name of the subroutine.

3. A label would be included in an assembler directive which specifies the location in memory corresponding to a symbol. This applies only to the directives: FCB FCC FDB

When used for this purpose, the label in the assembler directive would be identical with the corresponding symbol.

A label must be used in a statement which includes the assembler directive EQU. The label will be identical with the symbol which the EQU statement is defining.

5. In other cases, a label may be used in any executable instruction at the option of the programmer. Among the assembler directives EQU must always be written with a label; each of FCB, FCC, FDB, and RMB, may have a label; any other of the assembler directives must not be written with a label.

(For further details on the assembler directives see Appendix B.)

# Operator Field

The mnemonic operators recognized by the assembler include 72 executable instructions. Each instruction is translated by the assembler into one to three bytes of machine code. The remaining mnemonic operators are assembler directives, of which four (FCB, FCC, FDB, and RMB) are translated into one or more bytes of machine code. The other assembler directives control the overall assembly process and are not translated individually into machine code.

A functional classification of the mnemonic operators is shown in Figure 3-3. An alphabetical listing of the executable instructions is given, with brief definitions, in Figure 3-4.

# Executable Instructions

Each of the executable instructions recognized in the source language consists of three alphabetic characters. (However, as when the first operand in the operand field is either A or B, the programmer has the option of joining the character A or B to the operator, which results in an apparent four-character format.)

Figure 3-2 gives complete information stating which modes of addressing can be used with the different executable instructions. The table also shows the execution times in clock cycles.

The assembly of an executable instruction results in from one to three bytes of machine code, depending on the addressing mode. This information is summarized in Figure 3-5.

Detailed definitions of the executable instructions are given in Appendix A.

| I.   | Ope                              | rations on 8-Bit Registers:                                                                                   |

|------|----------------------------------|---------------------------------------------------------------------------------------------------------------|

|      | A.<br>B.<br>C.<br>D.<br>E.<br>F. | Shifts and Rotations                                                                                          |

| II.  | Jum                              | p and Branch Control:                                                                                         |

|      | A.                               | Conditional BranchBCC BCS BEQ BGE BGT BHI BLE BLS BLT BMI BNE BPL BVC BVS                                     |

|      | B.<br>C.<br>D.                   | Unconditional Branch and Jump .BRA NOP JMP Control of SubroutinesBSR JSR RTS Control of InterruptsRTI SWI WAI |

| III. | Con                              | trol of Index Register and Stack Pointer:                                                                     |

|      | A.<br>B.<br>C.                   | 5 mon 1 5 mon 2 5 5 6 7 6 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                       |

| IV.  | Con                              | trol of Condition Codes Register:                                                                             |

|      | A.<br>B.                         | Bit Control                                                                                                   |

| V.   | Asse                             | embler Directives                                                                                             |

Figure 3-3 Functional Classification of the Mnemonic Operators

| ABA | Add Accumulators                | INS        | Increment Stack Pointer                      |

|-----|---------------------------------|------------|----------------------------------------------|

| ADC | Add with Carry                  | INX        | Increment Index Register                     |

| ADD | Add                             | JMP        | Jump                                         |

| AND | Logical And                     | JSR        | Jump to Subroutine                           |

| ASL | Arithmetic Shift Left           |            |                                              |

| ASR | Arithmetic Shift Right          | LDA        | Load Accumulator                             |

| BCC | Branch if Carry Clear           | LDS        | Load Stack Pointer                           |

| BCS | Branch if Carry Set             | LDX        | Load Index Register                          |

| BEQ | Branch if Equal to Zero         | LSR        | Logical Shift Right                          |

| BGE | Branch if Greater or Equal Zero | NEG        | Negate                                       |

| BGT | Branch if Greater than Zero     | NOP        | No Operation                                 |

| BHI | Branch if Higher                | ORA        | Inclusive OR Accumulator                     |

| BIT | Bit Test                        |            | inclusive OH Accumulator                     |

| BLE | Branch if Less or Equal         | PSH        | Push Data                                    |

| BLS | Branch if Lower or Same         | PUL        | Pull Data                                    |

| BLT | Branch if Less than Zero        | ROL        | Rotate Left                                  |

| BMI | Branch if Minus                 | ROR        | Rotate Right                                 |

| BNE | Branch if Not Equal to Zero     | RTI        | Return from Interrupt                        |

| BPL | Branch if Plus                  | RTS        | Return from Subroutine                       |

| BRA | Branch Always                   |            |                                              |

| BSR | Branch to Subroutine            | SBA        | Subtract Accumulators                        |

| BVC | Branch if Overflow Clear        | SBC        | Subtract with Carry                          |

| BVS | Branch if Overflow Set          | SEC        | Set Carry                                    |

| CBA | Compare Accumulators            | SEI        | Set Interrupt Mask                           |

| CLC | Clear Carry                     | SEV        | Set Overflow                                 |

| CLI | Clear Interrupt Mask            | STA        | Store Accumulator                            |

| CLR | Clear                           | STS<br>STX | Store Stack Register                         |

| CLV | Clear Overflow                  | SUB        | Store Index Register Subtract                |

| CMP | Compare                         | SWI        | +                                            |

| COM | Complement                      |            | Software Interrupt                           |

| CPX | Compare Index Register          | TAB        | Transfer Accumulators                        |

| DAA | Decimal Adjust                  | TAP        | Transfer Accumulators to Condition Code Reg. |

| DEC | Decimal Adjust                  | TBA        | Transfer Accumulators                        |

| DES | Decrement Stack Pointer         | TPA        | Transfer Condition Code Reg. to Accumulator  |

| DEX | Decrement Index Register        | TST        | Test                                         |

|     |                                 | TSX        | Transfer Stack Pointer to Index Register     |

| EOR | Exclusive OR                    | TXS        | Transfer Index Register to Stack Pointer     |

| INC | Increment                       | WAI        | Wait for Interrupt                           |

|     |                                 |            | •                                            |

Figure 3-4 Executable Instructions -- Alphabetic List

| ADDRESSING MODE                            | NUMBER OF BYTES<br>OF MACHINE CODE |

|--------------------------------------------|------------------------------------|

| Inherent                                   | 1                                  |

| Accumulator (single operand)               | 1 .                                |

| Relative                                   | 2                                  |

| Direct                                     | 2                                  |

| Indexed                                    | 2                                  |

| Immediate:                                 | 2                                  |

| 1. All instructions except CPX, LDS and LD | 2                                  |

| 2. Instructions CPX, LDS and LDX           | 3                                  |

| Extended                                   | 3                                  |

|                                            |                                    |

Figure 3-5

# Operand Field

The kind of information placed in the operand field depends on the particular mnemonic operator. For the 72 executable instructions the microprocessor uses various modes of addressing for obtaining the operands and saving the results of execution. The addressing mode is determined by the mnemonic operator combined with the information in the operand field. The addressing modes are summarized in Figure 3-2.

The assembler recognizes numbers, symbols and expressions in the operand field. Dual operand instructions require either of the single characters A or B as the first operand.

# Numbers

Numbers are accepted by the assembler in the following formats:

| Number               | (decimal)     |

|----------------------|---------------|

| <pre>\$ Number</pre> | (hexadecimal) |

| Number H             | (hexadecimal) |

| 0 Number             | (octal)       |

| Number 0             | (octal)       |

| Number Q             | (octal)       |

| % Number             | (binary)      |

| Number B             | (binary)      |

where Number is a positive integer. A prefix "\$", "@", or "%" instructs the assembler to interpret the number as hexadecimal, octal, or binary, respectively. A suffix of "O" or "Q" indicate octal numbers while the suffix "H" indicates hexadecimal, and the suffix "B" indicates binary. When none of these prefixes or suffixes is used, the number is assumed to be decimal.

In the case where the prefix is "\$" and the last character is "B" the assembler interprets the number as hexadecimal.

Symbols 8 8 1

Symbols when used in the operand field follow these rules.

- 1. A symbol must not be any of the single characters A, B, or X.

- 2. Subject to rule (1), a symbol may consist of from 1 to 6 alphanumeric characters, of which the first is alphabetic. The single character "\*" is a symbol which represents the

- program counter.

The special symbol "\*" represents the program counter. Its value is, therefore, equal to the numerical address of the first byte of machine code which results from the assembly of any source instruction which contains "\*" in the operand field.

The single characters A, B, and X are reserved for special use in the source program, to represent accumulator A, accumulator B, and the index register. The single characters A or B must be used with dual operand instructions and may be used to indicate accumulator addressing. The single character X is indication of indexed addressing.

All other symbols must be defined in the source program. There are three ways of defining a symbol, as follows:

- 1. An executive instruction in the source program may include a label indentical with the symbol being defined. The value of the symbol is then the numerical address of the first byte of machine code which results from the executive instruction which includes the label.

- 2. One of the assembler directives FCB, FCC, FDB, or RMB may be written with a label identical with the symbol being defined. The value of the symbol is then the numerical address of the first byte of machine code which results from the assembler directive (FCB, FCC, FDB, or RMB) which includes the label.

- The symbol may be defined by using the assembler directive EQU. The mnemonic operator "EQU" is preceded by a label identical with the symbol being defined. The value of the symbol, represented by the label, is that of the operand which follows the mnemonic operator "EQU". The operand may be a number, another symbol, or an expression.

# Expressions

An expression is a combination of symbols and/or numbers being separated one from the next by one of the arithmetic operators (+, -, \*, or /).

The assembler evaluates expressions algebraically from left to right without parenthetical grouping, there being no heirarchy of precedence among the arithmetic operators. A fractional result, or intermediate result, if obtained during the evaluation of an expression, will be truncated to an integer value. The use of expressions in the source language does not imply any capability of the microprocessor to evaluate those expressions, since the expressions are evaluated during assembly and not during execution of the machine language program.

1

### Evaluation of Symbols and Expressions

The assembler must complete the numerical evaluation of symbols and expressions in two passes through a source program. Reflecting the two-pass characteristic of the assembly process, only one level of forward referencing is permitted in the use of symbols or expressions in the operand field of source statements.

#### Comments Field

A comment may be included in a source statement at the option of the programmer. The comment, if present, may contain any characters corresponding to ASCII hexadecimal values 20 (SP) through 5F (\_\_\_). Source statement comments do not affect the machine code which results from the assembly of a program. They are ignored by the assembler except for being included in the program listing.

Comments may be used in source programs for aiding comprehension of the program, and for purposes of checkout and documentation.

# ADDRESSING MODES

The assembler scans the operator and operand to determine the proper addressing mode. The addressing modes are:

Inherent Addressing Relative Addressing Immediate Addressing Indexed Addressing Accumulator Addressing Extended Addressing Direct Addressing Dual Addressing

Eleven of the executable instructions require addressing of two operands in the operand field. These instructions are indicated in Figure 3-2 by the column headed "Dual Operand". For all of these operators the first operand must be either accumulator A or accumulator B. This is specified respectively by A or B as the first character in the operand field, the second character in the operand field being a SPACE (OR TAB).

For dual addressing the specification of the first operand (either A or B) is separated from that of the second operand by one or more SPACE characters (or alternatively by TAB).

The second operand is specified in the operand field in accordance with the rules for immediate, direct, extended, or indexed addressing (as defined subsequently); depending on which modes of addressing are valid for the individual operators.

(For the mnemonic operators which employ dual addressing it is permissible to omit the SPACE between the operator and the operand field.)

Accumulator Addressing (single operand)

Thirteen of the operators address a single operand from the operand field and can so address either accumulator A or accumulator B in the microprocessing unit. These operators are indicated by the column headed "ACCX" in Figure 3-2. This mode of addressing is specified by writing an operand field consisting only of the single character A or B, corresponding to accumulator A or accumulator B. (It is then permissible to omit the SPACE (or TAB) between the operator and the operand field, for this type of addressing.)

For this type of addressing the assembly of a source instruction results in one byte of instruction in the machine language.

(For operators PUL and PSH, the accumulator mode is the only valid mode of addressing. The remaining eleven operators capable of this mode of addressing can alternatively be used with extended or indexed addressing.)

Inherent Addressing

In many cases the mnemonic operator itself specifies one or more registers which contain operands or in which results are saved. For example, the operator ABA requires two operands which are located in accumulator A and accumulator B of the microprocessor. The operator also determines that the result of execution will be saved in accumulator A.

For some executable instructions, all of the information which may be required for the addressing is contained in the mnemonic operator, and no operand field is used in the source statement. There are 25 such instructions. These are indicated by the column headed "inherent" in Figure 3-2.

Assembly of this type of source instruction results in only one byte of machine language code. (Some other operators which contain addressing information inherently in the mnemonic code also require further addressing or operand information which is then placed in an operand field. Examples are the operators CPX, LDS, LDX, STS, and STX.)

Immediate Addressing

The operators with which the immediate mode of addressing is permissible are indicated by the column headed "immediate" in Figure 3-2. This mode of addressing is selected by beginning the specification of the corresponding operand (in the operand field of a source statement) with the pound character "#".

With the immediate mode of addressing, the operand field of the source statement either contains the actual value of the operand, or it includes a symbol or an expression which has an algebraic value equal to the value of the operand. The operand may be specified in accordance with any of the following formats:

- # Number

# Symbol

- # Expression

- יר י

In the first three of these alternate forms the assembler will find or compute a numerical value of the operand. For any executive instruction in the immediate mode of addressing except CPX, LDS, or LDX, the numeric value must be an integer from 0 to 255 (decimal). For the operators CPX, LDS, or LDX, any value from 0 to 65535 (decimal) is valid.

In the last of the alternative forms, #'C, the apostrophe instructs the Assembler to translate the next character into the corresponding 7-bit ASCII code. The ASCII code so obtained is then the value of the operand. The single character "C" can be any character of the ASCII character set with hexadecimal value from 20 (SP) through 5F (\_\_\_\_).

For the immediate mode of addressing, the assembler inserts the actual value of the operand into the machine code. Except for the three operators CPX, LDS, and LDX an instruction in the immediate mode is assembled into two bytes of machine code, and the value of the operand is entered in the second byte. When it is a number, the operand is entered in the memory in unsigned 8-bit binary code. When it is an ASCII character, the corresponding 7-bit ASCII code applies, using bits 0-6, and bit 7 is set to zero.

For the three operators CPX, LDS, or LDX, used in the immediate mode, the source statement is assembled into three bytes of machine code. The numerical operand, which can have any value from 0 through FFFF, will be entered in the second and third bytes. The second byte will contain the most significant part of the operand, the third byte will contain the least significant part of the operand. Both parts are entered into the respective bytes of the memory in unsigned 8-bit binary code.

The operators CPX, LDS, or LDX, in the immediate mode, are not normally used with an operand in the format "#'C". However, in such a case, the assembler would place the ASCII coded character "C" in the third byte of the machine code corresponding to the source instruction.

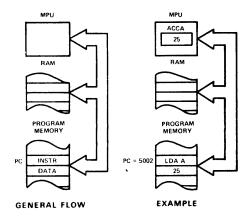

When the immediate mode of addressing is used, the numerical address is in effect that of the second byte of machine code which results from assembly of the source instruction. Data flow for the immediate addressing mode is shown in Figure 3-6.

Figure 3-6 Immediate Addressing

Mode Data Flow

Relative Addressing

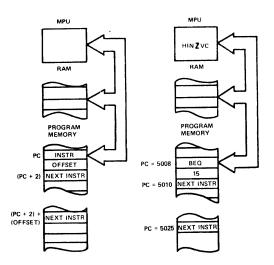

For the relative addressing mode to be valid, there is a rule which limits the distance in the machine language program from the branch instruction to the destination of the branch. The rule which applies to the relative addressing mode is that the address of the destination of the branch must be within the range specified by:

(PC + 2) - 128 < D < (PC + 2) + 127

where:

PC = address of the first byte of the branch instruction D = address of the destination of the branch instruction.

When it is desired to transfer control beyond the range of the branch instructions, this can be done by using JMP (unconditional jump) or JSR (jump to subroutine). These instructions do not use the relative mode of addressing.

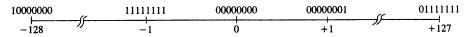

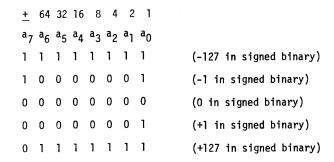

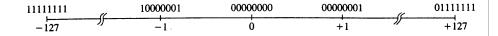

The assembler translates a branch instruction into two bytes of the machine code. The second byte contains a relative address. This is stored as a number in 8-bit, two's complement, binary form, with decimal value in the range from -128 to +127. These numbers correspond to the limits of the range of a branch instruction, as described above.

The relationship between the relative address and the absolute address of the destination of a branch instruction is expressed by:

D = (PC + 2) + R

where:

PC = address of first byte of the branch instruction

D = address of the destination of the branch instruction

R = the 8-bit, two's complement, binary number, stored in the second byte of the branch instruction.

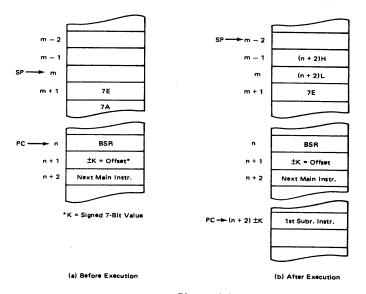

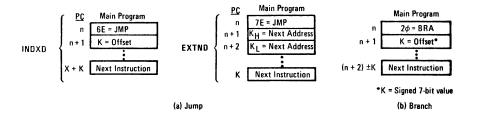

The relative addressing mode is available only to the conditional branch instructions, the unconditional branch instruction BRA, and the branch to subroutine BSR. None of these source instructions can use any other mode of addressing. The three-character mnemonic instruction is, therefore, sufficient to determine for the assembler when the relative mode of addressing will be used. An example of the data flow for the relative addressing mode is shown in Figure 3-7.

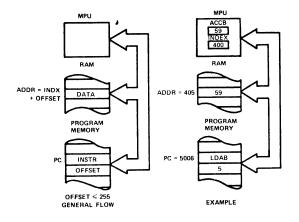

Indexed Addressing

A column of Figure 3-2 indicates the instructions for which indexed addressing is valid.

With this mode of addressing, the numerical address is variable and dependent on the contents of the index register. The current address is obtained whenever it is required during the execution of a program, rather than being pre-determined by the assembler as it is for the other addressing modes. The operand field of the source statement contains a numerical value which, when added to the contents of the index register during execution of the program, will provide the numerical address. Alternatively the operand field may contain a symbol or an expression which the assembler is able to replace by the value which is to be added to the contents of the index register. An example of the indexed addressing mode is shown in Figure 3-8.

For indexed addressing the data for obtaining the numerical address may be written in any of the formats:

X ,X Number,X Symbol,X Expression,X

è

Figure 3-7 Relative Addressing Mode Data Flow

Figure 3-8 Indexed Addressing Mode

The single character "X" informs the assembler that the indexed mode is to be used, the character "X" being reserved to denote the index register.

The format "X", when used alone, instructs the assembler that the address of the operand is identical with the contents of the index register. (This format has the same effect on the assembly as if "0,X" had been written.)

If a symbol or an expression is used rather than a number, the assembler will find or compute a numerical value of that symbol or expression. The source program must then include other statements which define a numerical value for the symbol or which enable the assembler to compute a numerical value for the symbol or expression. Only values from zero to FF (hexadecimal) are valid. This value is added to the contents of the index register during execution to obtain the numerical address as shown in the following formula:

D = numerical value + X where

X = contents of index register

D = numerical address

For indexed addressing the source instruction is translated into two bytes of the machine code. The second byte contains the number, in unsigned 8-bit binary form, which is added during execution of the instruction to the contents of the index register. The number thus obtained is the numerical address (in accordance with the foregoing formula).

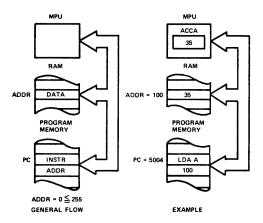

Direct and Extended Addressing

For direct addressing the source instruction is translated into two bytes of machine code. The second byte will contain the address in unsigned 8-bit binary form.

For extended addressing the source instruction is translated into three bytes of machine language. The second of these bytes will contain the highest 8 bits of the address. The third byte will contain the lowest 8 bits of the address. The contents of the second and third bytes will both be coded in unsigned 8-bit binary form.

For both direct and extended addressing, the address, which is placed by the assembler into the second or the second and third bytes of the machine code, is the absolute numerical address.

As may be seen in Figure 3-2, there are several instructions for which the extended mode of addressing is valid but the direct mode is not. For these instructions, when using any of the following formats,  $\frac{1}{2}$

Number Symbol

Expression the assembler will select the extended mode of addressing whatever may be the value of the numerical address. The source statement will be translated into three bytes of the machine code.

For those instructions which may use the direct mode of addressing as well as the extended mode, the assembler selects the mode according to the following rule: The assembler will select direct addressing if the numerical address is in the range from zero to 255 (decimal) and will select extended addressing if the numerical address exceeds 255 (decimal). Examples of the direct and extended addressing modes are shown in Figures 3-9 and 3-10.

Figure 3-9 Direct Addressing Mode Data Flow

Figure 3-10 Extended Addressing Mode Data Flow

# ASSEMBLER DIRECTIVES

The assembler directives allow the programmer control of the assembly of the executive instructions into machine code, including control of the allocation of memory, and assignment of values to data, when applicable. The assembler directives also provide for control of the sequencing of source programs through the assembler, and for control of the format of the assembler output.

A functional classification of the assembler directives is given below:

| CODE                      | SUMMARY DEFINITION                                                                                                               | FUNCTION                                                                                       |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ORG                       | Assign origin of program counter                                                                                                 | Defines the numerical address of the first byt of a subsequent segment the coded program.      |

| EQU                       | Equate a symbol to an operand                                                                                                    | Equates a symbol to a nu<br>merical value, another<br>symbol, or an expression                 |

| FCB<br>FCC<br>FDB<br>RMB  | Form constant byte<br>Form constant characters<br>Form double constant byte<br>Reserve memory bytes                              | Assign values and<br>addresses of data, and<br>assign addresses of<br>scratch areas of memory. |

| END<br>MON                | Define end of source program<br>Return to console                                                                                | Control the sequencing of source programs through the assembler.                               |

| NAM<br>OPT<br>PAGE<br>SPC | Name the program or insert text<br>Assembler control options<br>Move paper to top of form<br>Vertical spacing of program listing | Format control<br>(Source program and/or<br>assembler listing)                                 |

Assembler Directives - Operand Formating

| FCB (2) EQU (1)<br>FDB (2) ORG (1)<br>RMB (1) SPC (1) | FCC<br>NAM<br>OPT                                                   | END<br>MON<br>PAGE                                                              |

|-------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Number                                                | Special Format-<br>ting Rules                                       | No<br>Operand                                                                   |

| Symbol<br>Expression                                  | (see details of<br>the assembler dir-<br>ectives in Appendix<br>B.) | (Operand field is left blank or will be treated by the assembler as a comment.) |

Notes: (1) Only one operand.

(2) May have more than one operand, separated by commas.

Labels Used with Assembler Directives

A label must be included in any source statement which includes the assembler directive "EQU". The label must be identical with a symbol used elsewhere in the source program. The "EQU" directive is used to define the symbol, directly or indirectly.

The significance of the label, in this case depends on that of the symbol with which it is identical. It can represent a numerical address, or data, or neither of these. In the latter case the label, and the corresponding symbol, would represent an algebraic quantity which appears in one or more expressions in the source program.

A label may be included in any source statement which includes any of the assembler directives FCB, FCC, FDB, or RMB. These are the only assembler directives which are translated individually into one or more bytes of machine code. The label, if used, represents the address of the first byte of the machine code which results from the respective source statement.

Any source statement which includes any assembler directive other than EQU, FCB, FCC, FDB or RMB, must not be written with a label.

Comments Used with Assembler Directives

The assembler directive "NAM" does not distinguish between the operand field and a comment. Both are treated by the assembler as continuous text.

A comment may be used with any other assembler directive at the option of the programmer; however, comments with the SPC or PAGE assembler directives will not be printed (these two directives do not print).

#### IV INSTRUCTION SET

The M6800 instructions are each described in detail in Appendix A. This section will provide a brief introduction to the instructions and discuss their use in writing 680b programs.

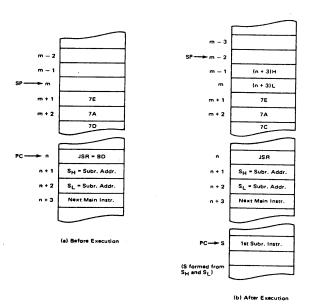

The instruction set is shown in summary form in Figure 4-1. Each of the 72 executable instructions of the source language assembles into from 1 to 3 bytes of machine code. The number of bytes depends on the particular instruction and on the addressing mode. The addressing modes which are available for use with the various executive instructions are indicated in Figure 3-2.

The coding of the first (or only) byte, corresponding to an executable instruction, is sufficient to identify the instruction and the addressing mode. The hexadecimal equivalents of the binary codes, which result from the translation of the 72 instructions, in all valid modes of addressing, are shown in Figure 4-2. There are 197 valid machine codes, 59 of the 256 possible codes being unassigned. The octal and decimal equivalents of the machine language codes are shown similarly, in Figures 4-3 and 4-4.

Microprocessor instructions are often divided into three general classifications: (1) memory reference, so called because they operate on specific memory locations; (2) operating instructions that function without needing a memory reference; (3) I/O instructions for transferring data between the microprocessor and peripheral devices.

In many instances, the 6800 performs the same operation on both its internal accumulators and the external memory locations. In addition, the M6800 treats peripheral devices exactly like memory locations, hence, no I/O instructions as such are required. Because of these features, other classifications are more suitable for introducing the 6800 instruction set: (1) Accumulator and memory operations; (2) Program control operations; (3) Condition Code Register operations.

## CONDITION CODE REGISTER OPERATIONS

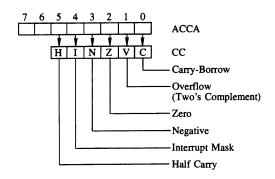

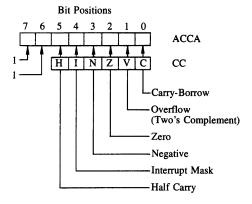

The Condition Code Register (CCR), also called the Program Status Byte, will be described first since it is affected by many of the other instructions as well as the specific operations shown in Figure 4-6. The CCR is a 6-bit register within the MPU that is useful in controlling program flow during system operation. The bits are defined in Figure 4-5-

The instructions shown in Figure 4-6 are available to the user for direct manipulation of the CCR. In addition, the MPU automatically sets or clears the appropriate status bits as many of the other instructions are executed. The effect of those instructions on the condition code register will be indicated as they are introduced and is also included in the Instruction Set Summary of Figure 4-1.

|                                      |              | _   |     |    |     |      |     | DDRE    |     |     | DES |     |    |          |     |     | BOOLEAN/ARITHMETIC OPERATION                              | c   | ONI | D. CC | DE  | RE       | 6.       |

|--------------------------------------|--------------|-----|-----|----|-----|------|-----|---------|-----|-----|-----|-----|----|----------|-----|-----|-----------------------------------------------------------|-----|-----|-------|-----|----------|----------|

| ACCUMULATOR AND                      | MEMORY       | L   | IMM | ED | _   | DIRE | CT  | $\perp$ | IND | EX  |     | EXT | ND |          | INH | ER  | (All register labels                                      | 5   | 4   | 3     | 2   | 1        | •        |

| OPERATIONS                           | MNEMONIC     | OP. | -   | #  | OP  | ~    | #   | OP      | ~   | #   | OP  | -   | #  | OP       | ~   | #   | refer to contents)                                        | H   | ī   | N     | Z   | v        | C        |

| Add                                  | ADDA         | 88  | 2   | 2  | 98  | 3    | 2   | AB      | 5   | 2   | 88  | 4   | 3  | T        | Γ   | Г   | A+M→A                                                     | 1   | •   | 1     | 1   | 1        | 1        |

|                                      | ADDB         | СВ  | 2   | 2  | DB  | 3    | 2   | EB      | 5   | 2   | FB  | 4   | 3  | 1        |     |     | B + M → B                                                 | 1   |     | 1     | 1   | :        | 1        |

| Add Acmitrs                          | ABA          |     |     | 1  |     |      |     | 1       |     | 1   |     |     |    | 18       | 2   | 1   | A+B→A                                                     | 1   | •   | 1     | :   | :        | :        |

| Add with Carry                       | ADCA         | 89  | 2   | 2  | 99  | 3    | 2   | A9      | 5   | 2   | 89  | 4   | 3  | 1        |     |     | A+M+C→A                                                   | 1   | •   | 1     | t   | :        | <b>:</b> |

|                                      | ADCB         | C9  | 2   | 2  | D9  | 3    | 2   | E9      | 5   | 2   | F9  | 4   | 3  |          |     |     | B + M + C → B                                             | t   | •   | 1     | :   | :        | 1        |

| And                                  | ANDA         | 84  | 2   | 2  | 94  | 3    | 2   | A4      | 5   | 2   | B4  | 4   | 3  | 1        |     |     | A · M · · A                                               | •   | •   | :     | 1   | R        | •        |

|                                      | ANDB         | C4  | 2   | 2  | D4  | 3    | 2   | E4      | 5   | 2   | F4  | 4   | 3  |          |     |     | B • M → B                                                 | •   | •   | 1     | 1   | R        | •        |

| Bit Test                             | BITA         | 85  | 2   | 2  | 95  | 3    | 2   | A5      | 5   | 2   | B5  | 4   | 3  |          |     |     | A • M                                                     | •   | •   | :     | 1   | R        | •        |

| •                                    | BITB         | C5  | 2   | 2  | 05  | 3    | 2   | E5      | 5   | 2   | F5  | 4   | 3  | 1        |     |     | B • M                                                     | •   | •   | 1     | 1   | R        | •        |

| Clear                                | CLR          | l   | 1   | 1  | 1   | l    |     | 6F      | 7   | 2   | 7F  | 6   | 3  | ł        |     | 1   | 00 → M                                                    | •   | •   | R     | S   | R        | R        |

|                                      | CLRA         |     |     |    | ľ   |      |     | 1       | 1   |     | 1   | 1   | !  | 4F       | 2   | 1   | 00 →A .                                                   | •   | •   | R     | S   | R        | R        |

| •                                    | CLRB         | ١   | ١.  | ١. | ١   | ١.   | ١.  | ١       | ١.  |     | l   | ١.  | ١. | 5F       | 2   | 1   | 00 →B                                                     | •   | •   | R     | s   | R        | R        |

| Compare                              | CMPA         | 81  | 2   | 2  | 91  | 3    | 2   | A1      | 5   | 2   | B1  | 4   | 3  | l        |     |     | A - M                                                     | •   | •   | :     | 1   | :        | :        |

| C A                                  | CMPB         | C1  | 2   | 2  | 01  | 3    | 2   | E1      | 5   | 2   | F1  | 4   | 3  | l        |     |     | B - M                                                     | •   | •   | 1     | 1   | 1        | 1        |

| Compare Acmitrs                      | CBA          | 1   |     |    | 1   |      | l   |         | ١.  | ١.  | l   | ١.  | ١. | 11       | 2   | 1   | A - B                                                     | •   | •   | 1     | 1   | ‡        | 1        |

| Complement, 1's                      | COM          |     | 1   |    | ı   |      | l   | 63      | 7   | 2   | 73  | 6   | 3  |          |     |     | M→M                                                       | •   | •   | *     | :   | R        | S        |

|                                      | COMA<br>COMB | 1   |     |    | ١.  |      | ı   | 1       | l   |     |     | i   | 1  | 43       | 2   | 1   | Ā→A                                                       | •   | •   | 1     |     | R        | s        |

| Complement, 2's                      | NEC          |     | ĺ   |    | 1   | l    | ]   | 0       | ١.  | ١.  |     | ١.  | ١. | 53       | 2   | 1   | B→B                                                       | •   | •   | 1     | 1   | R        | s        |

| (Negate)                             |              |     |     |    | 1   | 1    | l   | 60      | ١,  | 2   | 70  | 6   | 3  | ١        | . 1 |     | 00 - M → M                                                | •   | •   | 1     | 1   | Õ        | 13       |

| (megane)                             | NEGA<br>NEGB | Ì   |     |    | 1   |      | 1   |         | 1   |     | 1   |     | 1  | 40<br>50 | 2   | 1   | 00 ~ A → A                                                | •   | •   | :     | :   |          | 3        |

|                                      |              |     |     |    |     |      |     | l       |     |     | 1   |     |    |          | - 1 | 1   | 00 - B → B                                                | •   | •   |       |     | ଡା       | @        |

| Decimal Adjust, A                    | DAA          |     | i   | 1  |     | 1    | ļ   | 1       | l   |     | 1   | 1   | 1  | 19       | 2   | 1.  | Converts Binary Add. of BCD Characters<br>into BCD Format | •   | •   | :     | :   | :        | 3        |

| Decrement                            | DEC          | Į   | Į   | 1  | l   |      | l   | 6A      | 7   | 2   | 7A  | 6   | 3  |          |     |     | M = 1 → M                                                 |     |     | 1     | :   | 0        | •        |

|                                      | DECA         | 1   | 1   |    | 1   | ł    |     |         |     |     |     |     |    | 4A       | 2   | 1   | A – 1 → A                                                 |     |     | 1     |     | ŏ        |          |

|                                      | DECB         |     |     | }  | 1   |      |     |         |     |     |     |     |    | 5A       | 2   | 1   | B 1 -> B                                                  |     |     | :     |     | ŏ        |          |

| Exclusive OR                         | EORA         | 88  | 2   | 2  | 98  | 3    | 2   | A8      | 5   | 2   | 88  | 4   | 3  |          |     |     | A⊕M→A                                                     |     |     | 1     | 1   | R        |          |

|                                      | EORB         | C8  | 2   | 2  | 08  | 3    | 2   | E8      | 5   | 2   | F8  | 4   | 3  |          |     |     | 8 ⊕ M → B                                                 |     |     | :     | 1   | R        |          |

| Increment                            | INC          |     | 1   |    |     |      |     | 60      | 7   | 2   | 7C  | 6   | 3  |          | . 1 |     | M+1→M                                                     |     |     | :     |     | 0        |          |

|                                      | INCA         |     |     |    | ĺ   |      |     |         |     |     |     | 1   |    | 4C       | 2   | 1   | A+1→A                                                     |     |     | 1     |     | ٥        |          |

|                                      | INCB         |     |     | l  |     | i I  |     |         |     | ١.  |     |     |    | 5C       | 2   | 1   | B+1→B                                                     |     |     | :     |     | ٥        |          |

| Load Acmitr                          | LDAA         | 86  | 2   | 2  | 96  | 3    | 2   | A6      | 5   | 2   | В6  | 4   | 3  |          | 1   | - 1 | M→A                                                       | •   | •   | :     | 1   | Ř        | •        |

|                                      | LDAB         | C6  | 2   | 2  | D6  | 3    | 2   | E6      | 5   | 2   | F6  | 4   | 3  |          | - 1 | - 1 | M → B                                                     | •   | •   | :     | :   | R        | •        |

| Or, Inclusive                        | ORAA         | 8A  | 2   | 2  | 9A  | 3    | 2   | AA      | 5   | 2   | BA  | 4   | 3  |          |     | İ   | A+M→A                                                     | •   | •   | :     | ‡   | R        | •        |

|                                      | ORAB         | CA  | 2   | 2  | DA  | 3    | 2   | EA      | 5   | 2   | FA  | 4   | 3  |          | - 1 | ı   | B + M → B                                                 | •   | •   | :     | :   | R        | •        |

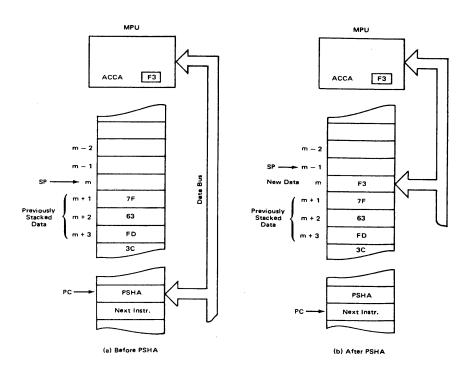

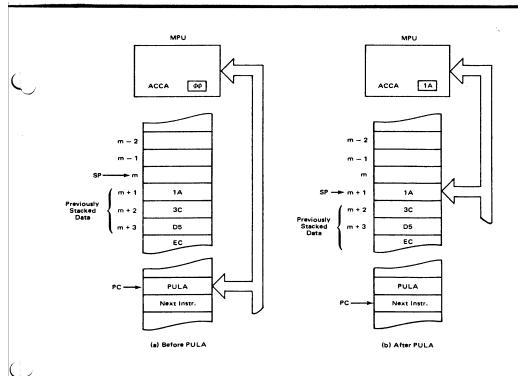

| Push Data                            | PSHA         |     |     | 1  |     |      |     |         |     |     |     |     |    | 36       | 4   | 1   | A → MSP, SP-1 → SP                                        | •   | •   | •     | •   | •        | •        |

|                                      | PSHB         |     |     | 1  |     |      |     |         |     |     |     |     |    | 37       | 4   | 1   | B → M <sub>SP</sub> , SP – 1 → SP                         | •   | •   | •     | •   | •        | •        |

| Puil Data                            | PULA         |     |     |    |     |      |     |         |     |     | 1 1 |     |    | 32       | 4   | 1   | SP + 1 → SP, MSP → A                                      | •   | •   | •     | •   | •        | •        |

|                                      | PULB         |     |     |    |     |      |     |         |     |     | ı   |     |    | 33       | 4   | 1   | SP + 1 → SP, M <sub>SP</sub> → B                          | •   | •   | •     | •   | •        | •        |

| Rotate Left                          | ROL          |     |     |    | 1   |      |     | 69      | 7   | 2   | 79  | 6   | 3  |          |     |     | M)                                                        | •   | •   | t     |     | ⊚        | :        |

|                                      | ROLA         |     |     |    |     |      | li  |         |     |     |     |     |    | 49       | 2   | 1   | v - chimin                                                | •   | •   | 1     |     | <b>©</b> | 1        |

|                                      | ROLB         |     |     |    | ļi  |      |     |         |     |     |     |     |    | 59       | 2   | 1   | B) 5 57 - 10                                              | •   | •   | 1     |     | <b>@</b> | :        |

| Actete Right                         | ROR          |     |     | ĺ  | li  |      |     | 66      | 7   | 2   | 76  | 6   | 3  |          |     |     | M                                                         | •   | •   | 1     |     | ⊚∣       | ‡        |

|                                      | RORA         |     |     |    |     |      |     |         |     |     |     |     |    | 46       | 2   | 1   | v} ~6 ~ tmin.tm                                           | •   | •   | :     |     | <b>©</b> | ‡        |

|                                      | RORB         | - 1 |     |    |     | ,    |     |         |     |     |     |     |    | 56       | 2   | 1   | B) 57 - 56                                                | •   | •   | ‡     |     | ⊚∣       | ‡        |

| Shift Left, Arithmetic               | ASL          | - 1 |     |    |     |      |     | 68      | '   | 2   | 78  | 6   | 3  |          | - 1 |     | M) -                                                      | •   | •   | 1     |     | ⊚∣       | 1        |

|                                      | ASLA         |     |     |    |     |      |     |         | i   |     |     |     |    | 48       | 2   | 1   | A                                                         | •   | •   | 1     |     | <b>©</b> | :        |

|                                      | ASLB         | 1   |     |    |     |      |     |         |     |     |     |     |    | 58       | 2   | 1   | в) — —                                                    | •   | •   | \$    |     | <b>©</b> | 1        |

| Shift Right, Arithmetic              | ASR          |     |     |    |     |      |     | 67      | 7   | 2   | 77  | 6   | 3  |          | ı   | - [ | M)                                                        | •   | •   | 1     |     | <b>©</b> | 1        |

|                                      | ASRA         | -   |     |    |     |      |     | 1       | ı   |     |     |     |    | 47       | 2   | 1   | v}                                                        | •   | •   | 1     |     | ⊚∣       | 1        |

|                                      | ASRB         | - 1 |     |    | 1   |      |     |         | - 1 |     |     |     |    | 57       | 2   | 1   | в) "                                                      | •   | •   | :     |     | ⊚∣       | :        |

| Shift Right, Logic.                  | LSR          | - 1 |     |    |     |      |     | 64      | 7   | 2   | 74  | 6   | 3  |          | - 1 | ٠.  | M} → .                                                    | •   | •   | R     | :   | ଭା       | :        |

|                                      | LSRA         | - 1 |     |    |     | ı    |     |         | - 1 | - 1 |     |     |    | 44       | 2   | 1   | A 0 → [] TITTE → Q                                        | •   | •   | R     |     | ⊚∣       | *        |

|                                      | LSRB         | - 1 |     |    |     |      | i   |         |     |     |     |     | li | 54       | 2   | 1   | B) "                                                      | •   | •   | R     | 1   | ⊚∣       | :        |

| Store Acmiti-                        | STAA         | !   |     |    | 97  | 4    | 2   | A7      | 6   | 2   | B7  | 5   | 3  |          | - 1 |     | A→M                                                       | •   | •   | :     | ‡   | R        | •        |

|                                      | STAB         | - 1 | 1   |    | D7  | 4    | 2   | E7      | 6   | 2   | F7  | 5   | 3  |          | - 1 | ł   | B → M                                                     | •   | •   | : [   | 1   | R        | •        |

| Subtract                             | SUBA         | 80  | 2   | 2  | 90  | 3    | 2   | A0      | 5   | 2   | В0  | 4   | 3  |          |     | 1   | A - M → A                                                 | •   | •   | :     | . 1 | :        | 1        |

|                                      | SUBB         | co  | 2   | 2  | DO  | 3    | 2   | E0      | 5   | 2   | FO  | 4   | 3  |          |     | - 1 | B - M → B                                                 | •   | •   | :     | - 1 | :        | 1        |

| Subract Acmitrs.                     | SBA          | - 1 |     |    |     |      | -   |         | - [ |     | 1   |     |    | 10       | 2   | 1   | A - B → A                                                 | •   | •   | :     | * [ | :        | :1       |

| Subtr. with Carry                    | SBCA         | 82  | 2   | 2  | 92  | 3    | 2   | A2      | 5   | 2   | 82  | 4   | 3  |          |     | ļ   | A - M - C → A                                             | •   | •   | \$    | :   | :        | :        |

|                                      | SBCB         | C2  | 2   | 2  | D2  | 3    | 2   | E2      | 5   | 2   | F2  | 4   | 3  |          |     |     | B - M - C → B                                             | •   | •   | :     | :   | :        | :        |

|                                      |              |     | - 1 |    | ı I | - 1  | - 1 | - 1     |     |     | 1   |     |    | 16       | 2   | 1   | A→B                                                       | •   | •   | :     | :   | R        | •        |

| Fransfer Acmitrs                     | TAB          | - 1 | - 1 |    |     |      | - 1 |         |     |     |     |     |    |          |     |     |                                                           |     |     |       |     |          |          |

| Fransfer Acmitrs                     | TAB<br>TBA   |     |     |    |     |      |     |         |     |     | - 1 |     |    | 17       | 2   | 1   | B→A                                                       | •   | •   | :     | :   | R        | •        |

| Fransfer Acmitrs Fest, Zero or Minus |              |     |     |    |     |      |     | 6D      | ,   | 2   | 70  | 6   | 3  | 17       | 2   | .1  | B → A<br>M – 90                                           |     | - 1 | :     | :   | R        | Ĥ        |

|                                      | TBA          |     |     |    |     |      |     | 6D      | ,   | 2   | 70  | 6   | 3  | 17<br>40 | 2   | 1   | 1                                                         | - 1 | •   | :     | :   | R        | A<br>R   |

Figure 4-1 M6800 Instruction Set

| INDEX REGISTER AND    | STACK    |    | IMMI | 0 |    | DIRE | CT | Π  | INDE | x |    | EXT | ND |    | INHI | R |                                                 | 5  | 4 | 3 | 2 | 1   | 0 |

|-----------------------|----------|----|------|---|----|------|----|----|------|---|----|-----|----|----|------|---|-------------------------------------------------|----|---|---|---|-----|---|

| POINTER OPERATIONS    | MNEMONIC | OP | ~    | # | OP | ~    | #  | OP | ~    | # | OP | ~   | #  | OP | ~    | # | BOOLEAN/ARITHMETIC OPERATION                    | н  | ı | N | Z | v   | С |

| Compare Index Reg     | CPX      | 8C | 3    | 3 | 90 | 4    | 2  | AC | 6    | 2 | ВС | 5   | 3  |    |      |   | $(X_H/X_L) = (M/M + 1)$                         | •  | • | 0 | : | (3) | • |